- 您现在的位置:买卖IC网 > Sheet目录1249 > TS-MAC-XM-UT4 (Lattice Semiconductor Corporation)SITE LICENSE ETH MAC TRI-SPD XP

�� �

�

Lattice� Semiconductor�

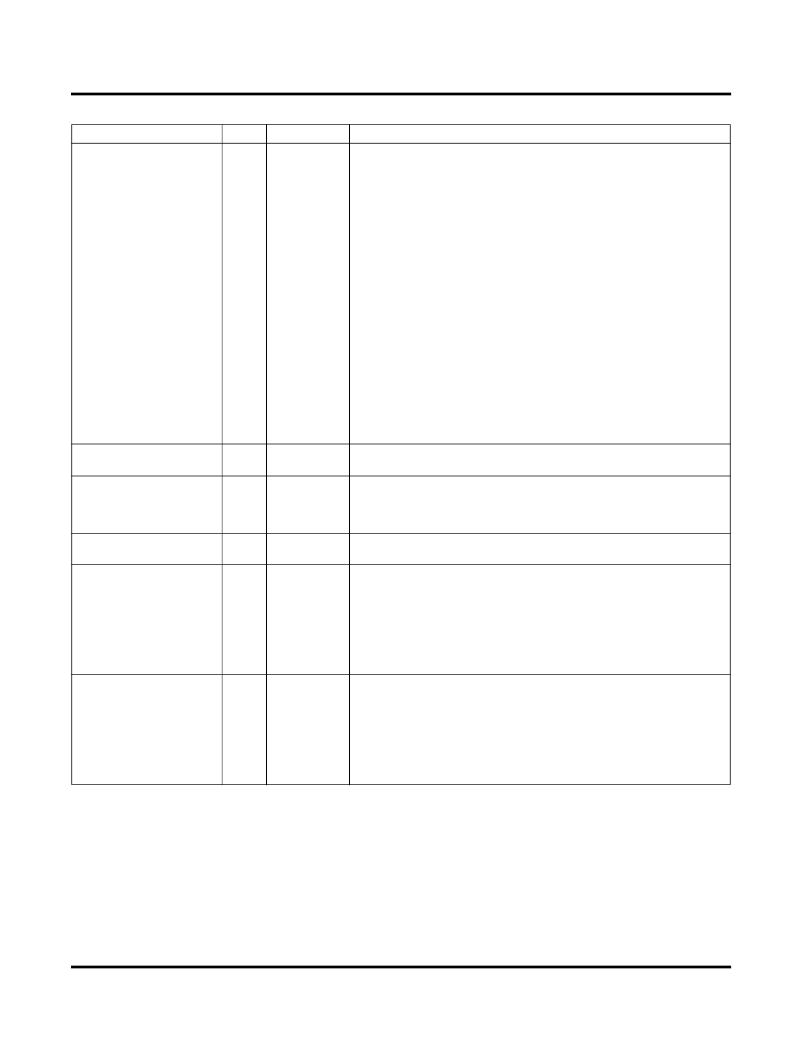

�Table� 2-1.� TSMAC� IP� Core� Input� and� Output� Signals�

�Functional� Description�

�Port� Name�

�Type�

�Active� State�

�Description�

�Receive� Statistics� Vector� .� This� bus� indicates� the� events� encountered�

�during� frame� reception.� This� bus� is� qualified� by� the� rx_stat_en� signal.�

�The� definition� of� each� signal� is� explained� in� the� Receive� MAC� section� of�

�this� user’s� guide.�

�The� corresponding� bit� locations� of� this� bus� are� defined� as� follows:�

�rx_statvec[15:0]� -� Frame� Byte� Count�

�rx_statvec[16]� -� VLAN� Tag� Detected�

�rx_statvec[17]� -� Pause� Frame�

�rx_statvec[18]� -� Control� Frame�

�tx_statvec[19]� -� Unsupported� Opcode�

�rx_stat_vector[31:0]�

�Output�

�N/A�

�rx_statvec[20]� -� Dribble� Nibble�

�rx_statvec[21]� -� Broadcast� Address�

�rx_statvec[22]� -� Multicast� Address�

�rx_statvec[23]� -� Receive� OK�

�rx_statvec[24]� -� Length� Check� Error�

�rx_statvec[25]� -� CRC� Error�

�rx_statvec[26]� -� Packet� Ignored�

�rx_statvec[27]� -� Carrier� Event� Previously� Seen�

�rx_statvec[28]� –� Unused�

�rx_statvec[29]� -� IPG� Violation�

�rx_statvec[30]� -� Short� Frame�

�rx_statvec[31]� -� Long� Frame�

�rx_stat_en�

�Output�

�High�

�Receive� Statistics� Vector� Enable� .� When� asserted,� this� signal� indicates�

�that� the� contents� of� the� rx_stat_vector� bus� is� valid.�

�Ignore� Next� Packet� .� This� signal� is� asserted� by� the� host� to� prevent� a�

�ignore_next_pkt�

�Input�

�High�

�Receive� FIFO� Full� condition.� The� Receive� MAC� continues� dropping�

�packets� as� long� as� this� signal� is� asserted.� This� is� an� asynchronous� sig-�

�nal.�

�rx_eof�

�Output�

�High�

�End� Of� Frame� .� Indicates� all� the� data� for� the� current� packet� has� passed�

�on� to� the� FIFO.�

�Receive� Packet� Error� .� When� asserted,� this� signal� indicates� the� packet�

�contains� error(s).� This� signal� is� qualified� with� the� rx_eof� signal.�

�The� rx_error� signal� will� be� asserted� for� any� of� the� following� three� condi-�

�rx_error�

�Output�

�High�

�tions:�

�?� The� rxer� signal� on� the� GMII� is� asserted� by� the� PHY� during� frame� recep-�

�tion.�

�?� There� are� Rx� FCS� errors� on� received� frames.�

�?� There� is� a� length� check� error� on� the� received� frame.�

�Receive� FIFO� Error� .� This� signal� is� asserted� when� the� external� Rx� FIFO�

�is� full� (rx_fifo_full� signal� asserted)� and� the� Rx� FIFO� is� being� written� to� by�

�the� Rx� MAC� (rx_write� is� asserted).� When� this� error� signal� is� asserted� the�

�rx_fifo_error�

�Output�

�High�

�rx_write� signal� will� be� de-asserted� as� long� as� the� rx_fifo_error� signal� is�

�asserted.� The� rx_fifo_error� signal� will� be� de-asserted� when� the� end� of�

�packet� (rx_eof)� exits� the� receive� FIFO� (Note:� for� this� errored� condition�

�data� will� continue� to� be� pulled� out� of� the� receive� FIFO,� even� while� the�

�rx_write� signal� has� been� de-asserted).�

�1.� Classic� TSMAC� IP� core� option.�

�2.� Gigabit� MAC� or� SGMII� Easy� Connect� MAC� options.�

�IPUG51_03.0,� December� 2010�

�18�

�Tri-Speed� Ethernet� MAC� User’s� Guide�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

TS250-130F-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-B-0.5-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-RB-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-RC-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-RC-B-0.5-2

POLYSWITCH PTC RESET 0.13A SMD

TS600-170F-2

POLYSWITCH PTC RESET 0.17A T/R

TS600-200F-RA-B-0.5-2

POLYSWITCH PTC RESET 0.20A SMD

TS600-400F-2

POLYSWITCH PTC RESET 0.40A SMD

相关代理商/技术参数

TSMBG0505C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|100V V(BO) MAX|DO-215AA

TSMBG0506C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|110V V(BO) MAX|DO-214AA

TSMBG0507C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|145V V(BO) MAX|DO-214AA

TSMBG0509C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|185V V(BO) MAX|DO-215AA

TSMBG0510C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|200V V(BO) MAX|DO-214AA

TSMBG0511C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|210V V(BO) MAX|DO-214AA

TSMBG0512C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|215V V(BO) MAX|DO-214AA

TSMBG0514C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|250V V(BO) MAX|DO-214AA